# DIGITALS ELECTRONICS IMPORTANT MCQ WITH SOLUTION

Q.1 The NAND gate output will be low if the two inputs are

**(A)** 00

**(B)** 01

**(C)** 10

**(D)** 11

Ans: D

The NAND gate output will be low if the two inputs are 11 (The Truth Table of NAND gate is shown in Table.1.1)

| X(Input) | Y(Input) | F(Output) |

|----------|----------|-----------|

| 0        | 0        | 1         |

| 0        | 1        | 1         |

| 1        | 0        | 1         |

| 1        | 1        | 0         |

Table 1.1 Truth Table for NAND Gate

Q.2 What is the binary equivalent of the decimal number 368

**(A)** 101110000

**(B)** 110110000

**(C)** 111010000

**(D)** 111100000

Ans: A

The Binary equivalent of the Decimal number 368 is 101110000 (Conversion from Decimal number to Binary number is given in Table 1.2)

| 2 | 368 |       |  |

|---|-----|-------|--|

| 2 | 184 | <br>0 |  |

| 2 | 92  | <br>0 |  |

| 2 | 46  | <br>0 |  |

| 2 | 23  | <br>0 |  |

| 2 | 11  | <br>1 |  |

| 2 | 5   | <br>1 |  |

| 2 | 2   | <br>1 |  |

| 2 | 1   | <br>0 |  |

|   | 0   | <br>1 |  |

Table 1.2 Conversion from Decimal number to Binary number

- Q.3The decimal equivalent of hex number 1A53 is

- (A) 6793

**(B)** 6739

**(C)** 6973

**(D)** 6379

Ans: B

The decimal equivalent of Hex Number 1A53 is 6739

(Conversion from Hex Number to Decimal Number is given below)

- Α  $16^{3}$  $16^{2}$

- 5  $16^{1}$

- 3 16°

Weights

Hexadecimal

$(1A53)_{16} = (1X16^3) + (10 X 16^2) + (5 X 16^1) + (3 X 16^0)$ = 4096 + 2560 + 80 + 3= 6739

- $(734)_8 = ()_{16}$ **Q.4**

- (A) C 1 D

**(B)** D C 1

**(C)** 1 C D

**(D)** 1 D C

Ans: D

$$(734)_8 = (1 D C)_{16}$$

$0001 \mid 1101 \mid 1100$

$1 D C$

- The simplification of the Boolean expression (ABC)+(ABC) is **Q.5**

- (A) 0

**(B)** 1

(C) A

**(D)** BC

Ans: B

The Boolean expression is

$$(ABC)+(ABC)$$

is equivalent to 1

$$(ABC)+(ABC)=A+\overline{B}+C+\overline{A}+B+\overline{C}=A+\overline{B}+C+\overline{A}+B+\overline{C}$$

$$=(A+\overline{A})(B+\overline{B})(C+\overline{C})=1X1X1=1$$

- The number of control lines for a 8 to 1 multiplexer is **Q.6**

- (A) 2

**(B)** 3

**(C)** 4

**(D)** 5

Ans: B

The number of control lines for an 8 to 1 Multiplexer is 3

(The control signals are used to steer any one of the 8 inputs to the output)

- **Q.7** How many Flip-Flops are required for mod–16 counter?

- (A) 5

**(B)** 6

**(C)** 3

**(D)** 4

Ans: D

The number of flip-flops is required for Mod-16 Counter is 4.

(For Mod-m Counter, we need N flip-flops where N is chosen to be the smallest number for which 2N is greater than or equal to m. In this case 24 greater than or equal to 1)

- Q.8 EPROM contents can be erased by exposing it to

- (A) Ultraviolet rays.

- **(B)** Infrared rays.

- (C) Burst of microwaves.

- **(D)** Intense heat radiations.

## Ans: A

EPROM contents can be erased by exposing it to Ultraviolet rays (The Ultraviolet light passes through a window in the IC package to the EPROM chip where it releases stored charges. Thus the stored contents are erased).

- Q.9 The hexadecimal number 'A0' has the decimal value equivalent to

- **(A)** 80

**(B)** 256

**(C)** 100

**(D)** 160

## Ans: D

The hexadecimal number 'A0' has the decimal value equivalent to 160

$$\begin{pmatrix} A & 0 \\ 16^1 & 16^0 = 10X16^1 + 0X16^0 = 160 \end{pmatrix}$$

- Q.10 The Gray code for decimal number 6 is equivalent to

- **(A)** 1100

**(B)** 1001

**(C)** 0101

**(D)** 0110

### Ans: C

The Gray code for decimal number 6 is equivalent to 0101 (Decimal number 6 is equivalent to binary number 0110)

- **Q.11** The Boolean expression  $\overline{A}$ **.**B + A**.**B is equivalent to

- (A) A + B

**(B)**  $\overline{A}$ .B

(C)  $\overline{A+B}$

**(D)** A.B

## Ans: A

The Boolean expression  $\overline{A} \cdot B + A \cdot \overline{B} + A \cdot B$  is equivalent to A + B  $(\overline{A} \cdot B + A \cdot \overline{B} + A \cdot B) = B(\overline{A} + A) + A \cdot \overline{B}$   $= B + A \cdot \overline{B} \{ (\overline{A} + A) = 1 \}$  $= A + B \{ (B + A \cdot \overline{B}) = B + A \}$

Q.12 The digital logic family which has minimum power dissipation is

**(A)** TTL

**(B)** RTL

(C) DTL

(D) CMOS

## Ans: D

The digital logic family which has minimum power dissipation is CMOS. (CMOS being an unipolar logic family, occupy a very small fraction of silicon Chip area)

- Q.13 The output of a logic gate is 1 when all its inputs are at logic 0. the gate is either

- (A) a NAND or an EX-OR

- (B) an OR or an EX-NOR

- (C) an AND or an EX-OR

- (D) a NOR or an EX-NOR

## Ans: D

The output of a logic gate is 1 when all inputs are at logic 0. The gate is either a NOR or an EX-NOR.

(The truth tables for NOR and EX-NOR Gates are shown in fig.1(a) & 1(b).)

| Input        |   | Output |

|--------------|---|--------|

| $\mathbf{A}$ | В | Y      |

| 0            | 0 | 1      |

| 0            | 1 | 0      |

| 1            | 0 | 0      |

| 1            | 1 | 0      |

| Input | Output |

|-------|--------|

| A B   | Y      |

| 0 0   | 1      |

| 0 1   | 0      |

| 1 0   | 0      |

| 1 1   | 1      |

Fig.1(a) Truth Table for NOR Gate Fig.1(b) Truth Table for EX-NOR Gate

- Q.14 Data can be changed from special code to temporal code by using

- (A) Shift registers

- **(B)** counters

- (C) Combinational circuits

- **(D)** A/D converters.

#### Ans: A

Data can be changed from special code to temporal code by using Shift Registers. (A Register in which data gets shifted towards left or right when clock pulses are applied is known as a Shift Register.)

- Q.15 A ring counter consisting of five Flip-Flops will have

- (A) 5 states

**(B)** 10 states

**(C)** 32 states

**(D)** Infinite states.

### Ans: A

A ring counter consisting of Five Flip-Flops will have 5 states.

- Q.16 The speed of conversion is maximum in

- (A) Successive-approximation A/D converter.

- **(B)** Parallel-comparative A/D converter.

- (C) Counter ramp A/D converter.

- **(D)** Dual-slope A/D converter.

### Ans: B

The speed of conversion is maximum in Parallel-comparator A/D converter (Speed of conversion is maximum because the comparisons of the input voltage are carried out simultaneously.)

- Q.17 The 2's complement of the number 1101101 is

- **(A)** 0101110

**(B)** 0111110

**(C)** 0110010

**(D)** 0010011

## Ans: D

The 2's complement of the number 1101101 is 0010011 (1's complement of the number 1101101 is 0010010

2's complement of the number 1101101is 0010010 + 1 =0010011)

- Q.18 The correction to be applied in decimal adder to the generated sum is

- **(A)** 00101

**(B)** 00110

**(C)** 01101

**(D)** 01010

## Ans: B

The correction to be applied in decimal adder to the generated sum is 00110.

When the four bit sum is more than 9 then the sum is invalid. In such cases, add +6(i.e. 0110) to the four bit sum to skip the six invalid states. If a carry is generated when adding 6, add the carry to the next four bit group.

- **Q.19** When simplified with Boolean Algebra (x + y)(x + z) simplifies to

- (A) x

**(B)** x + x(y + z)

**(C)** x(1 + yz)

**(D)** x + yz

### Ans: D

When simplified with Boolean Algebra (x + y)(x + z) simplifies to x + yz [(x + y) (x + z)] = xx + xz + xy + yz = x + xz + xy + yz ( xx = x)  $= x(1+z) + xy + yz = x + xy + yz \{ (1+z) = 1 \}$   $= x(1+y) + yz = x + yz \{ (1+y) = 1 \}$

- Q.20 The gates required to build a half adder are

- (A) EX-OR gate and NOR gate

- (B) EX-OR gate and OR gate

- (C) EX-OR gate and AND gate

- **(D)** Four NAND gates.

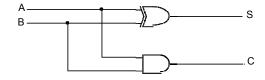

### Ans: C

The gates required to build a half adder are EX-OR gate and AND gate Fig.1(d) shows the logic diagram of half adder.

Fig.1(d) Logic diagram of Half Adder

- Q.21 The code where all successive numbers differ from their preceding number by single bit is

- (A) Binary code.

**(B)** BCD.

(C) Excess -3.

(D) Gray.

Ans: D

The code where all successive numbers differ from their preceding number by single bit is Gray Code.

(It is an unweighted code. The most important characteristic of this code is that only a single bit change occurs when going from one code number to next.)

- Q.22 Which of the following is the fastest logic

- (A) TTL

**(B)** ECL

(C) CMOS

**(D)** LSI

Ans: B

ECL is the fastest logic family of all logic families.

(High speeds are possible in ECL because the transistors are used in difference amplifier configuration, in which they are never driven into saturation and thereby the storage time is eliminated.

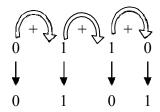

- Q.23 If the input to T-flipflop is 100 Hz signal, the final output of the three T-flipflops in cascade is

- **(A)** 1000 Hz

**(B)** 500 Hz

(C) 333 Hz

**(D)** 12.5 Hz.

Ans: D

If the input to T-flip-flop is  $100~\mathrm{Hz}$  signal, the final output of the three T- flip-flops in cascade is  $12.5~\mathrm{Hz}$

{The final output of the three T-flip-flops in cascade is

(T) =

$$\frac{Frequency}{2^N} = \frac{100}{2^3} = 12.5 \text{Hz}$$

- Q.24 Which of the memory is volatile memory

- (A) ROM

**(B)** RAM

(C) PROM

(D) EEPROM

Ans: B

RAM is a volatile memory

(Volatile memory means the contents of the RAM get erased as soon as the power goes off.)

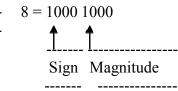

- **Q.25** -8 is equal to signed binary number

- **(A)** 10001000

**(B)** 00001000

**(C)** 10000000

**(D)** 11000000

Ans: A

- 8 is equal to signed binary number 10001000

(To represent negative numbers in the binary system, Digit 0 is used for the positive sign and 1 for the negative sign. The MSB is the sign bit followed by the magnitude bits. i.e.,

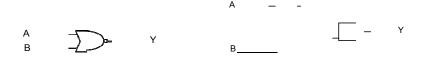

- Q.26 DeMorgan's first theorem shows the equivalence of

- (A) OR gate and Exclusive OR gate.

- **(B)** NOR gate and Bubbled AND gate.

- (C) NOR gate and NAND gate.

- (D) NAND gate and NOT gate

## Ans: B

DeMorgan's first theorem shows the equivalence of NOR gate and Bubbled AND gate (Logic diagrams for De Morgan's First Theorem is shown in fig.1(a)

Fig. 1(a) Logic Diagrams for De Morgan's First Theorem

- Q.27 The digital logic family which has the lowest propagation delay time is

- (A) ECL

(B) TTL

(C) CMOS

(D) PMOS

#### Ans: A

The digital logic family which has the lowest propagation delay time is ECL (Lowest propagation delay time is possible in ECL because the transistors are used in difference amplifier configuration, in which they are never driven into saturation and thereby the storage time is eliminated).

- Q.28 The device which changes from serial data to parallel data is

- (A) COUNTER

**(B)** MULTIPLEXER

**(C)** DEMULTIPLEXER

(D) FLIP-FLOP

## Ans: C

The device which changes from serial data to parallel data is demultiplexer. (A demultiplexer takes in data from one line and directs it to any of its N outputs depending on the status of the select inputs.)

- Q.29 A device which converts BCD to Seven Segment is called

- (A) Encoder

(B) Decoder

**(C)** Multiplexer

(D) Demultiplexer

### Ans: B

A device which converts BCD to Seven Segment is called DECODER. (A decoder coverts binary words into alphanumeric characters.)

- **Q.30** In a JK Flip-Flop, toggle means

- (A) Set Q = 1 and  $\overline{Q} = 0$ .

- **(B)** Set Q = 0 and  $\overline{Q} = 1$ .

- (C) Change the output to the opposite state.

- (D) No change in output.

## Ans: C

In a JK Flip-Flop, toggle means Change the output to the opposite state.

- Q.31 The access time of ROM using bipolar transistors is about

- (A) 1 sec

**(B)** 1 msec

(C) 1 usec

**(D)** 1 nsec.

## Ans: C

The access time of ROM using bipolar transistors is about 1  $\mu$  sec.

- Q.32 The A/D converter whose conversion time is independent of the number of bits is

- (A) Dual slope

- **(B)** Counter type

- (C) Parallel conversion

- **(D)** Successive approximation.

### Ans: C

The A/D converter whose conversion time is independent of the Number of bits is Parallel conversion.

(This type uses an array of comparators connected in parallel and comparators compare the input voltage at a particular ratio of the reference voltage).

- Q.33 When signed numbers are used in binary arithmetic, then which one of the following notations would have unique representation for zero.

- (A) Sign-magnitude.

- **(B)** 1's complement.

- **(C)** 2's complement.

- **(D)** 9's complement.

Ans: A

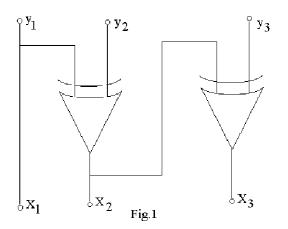

**Q.34** The logic circuit given below (Fig.1) converts a binary code  $y_1y_2$   $y_3$  into

(A) Excess-3 code.

(B) Gray code.

(C) BCD code.

(D) Hamming code.

## Ans: B

Gray code as

| X   | 1=Y1, | X2=Y | Y1 XOR Y2, | X3=Y | 1 XOR | Y2 XOR | Y3 |

|-----|-------|------|------------|------|-------|--------|----|

| For | Y1    | Y2   | Y3         | X1   | X2    | X3     |    |

|     | 0     | 0    | 0          | 0    | 0     | 0      |    |

|     | 0     | 0    | 1          | 0    | 0     | 1      |    |

|     | 0     | 1    | 0          | 0    | 1     | 1      |    |

|     | 0     | 1    | 1          | 0    | 1     | 0      |    |

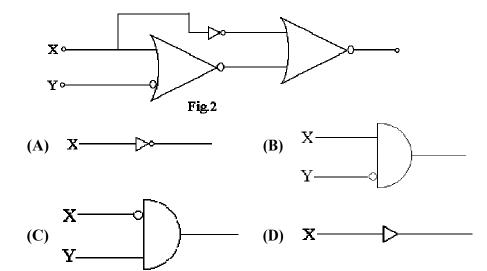

Q.35 The logic circuit shown in the given fig.2 can be minimised to

Ans: D

As output of the logic circuit is Y=(X+Y')'+(X'+(X+Y')')' (X+Y')'=X'Y Using DE Morgan's Now this is one of input of  $2^{nd}$  gate. F=(A+X')'=A'X=[(X'Y)'.X] =[(X+Y')X]=X+XY'=X(Y')=X

- Q.36 In digital ICs, Schottky transistors are preferred over normal transistors because of their

- **(A)** Lower Propagation delay.

- **(B)** Higher Propagation delay.

- **(C)** Lower Power dissipation.

- **(D)** Higher Power dissipation.

### Ans: A

Lower propagation delay as shottky transistors reduce the storage time delay by preventing the transistor from going deep into saturation.

Q.37 The following switching functions are to be implemented using a Decoder:

$$f_1 =$$

)  $m(1,2,4,8,10,14)$   $f_2 =$ )  $m(2,5,9,11)$   $f_3 =$ )  $m(2,4,5,6,7)$

9

The minimum configuration of the decoder should be

(A) 2 - to - 4 line.

- **(B)** 3 to 8 line.

- (C) 4 to 16 line.

- **(D)** 5 to 32 line.

Ans: C

4 to 16 line decoder as the minterms are ranging from 1 to 14.

- **Q.38** A 4-bit synchronous counter uses flip-flops with propagation delay times of 15 ns each. The maximum possible time required for change of state will be

- (A) 15 ns.

**(B)** 30 ns.

(C) 45 ns.

**(D)** 60 ns.

Ans: A

15 ns because in synchronous counter all the flip-flops change state at the same time.

- **Q.39** Words having 8-bits are to be stored into computer memory. The number of lines required for writing into memory are

- **(A)** 1.

**(B)** 2.

**(C)** 4.

**(D)** 8.

Ans: D

Because 8-bit words required 8 bit data lines.

**Q.40** In successive-approximation A/D converter, offset voltage equal to  $\frac{1}{2}$ LSB is added to the

D/A converter's output. This is done to

- (A) Improve the speed of operation.

- **(B)** Reduce the maximum quantization error.

- (C) Increase the number of bits at the output.

- (D) Increase the range of input voltage that can be converted.

Ans: B

- **Q.41** The decimal equivalent of Binary number 11010 is

- **(A)** 26.

**(B)** 36.

**(C)** 16.

**(D)** 23.

Ans: A

$$11010 = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 = 26$$

- Q.42 1's complement representation of decimal number of -17 by using 8 bit representation is

- **(A)** 1110 1110

**(B)** 1101 1101

**(C)** 1100 1100

**(D)** 0001 0001

Ans: A

$$(17)_{10} = (10001)_2$$

In 8 bit = 00010001

1's Complement = 11101110

| Q.43  | The excess 3 code of decimal number 26 is (A) 0100 1001 (B) 01011001     |                                                               |  |  |

|-------|--------------------------------------------------------------------------|---------------------------------------------------------------|--|--|

|       | (C) 1000 1001                                                            | <b>(D)</b> 01001101                                           |  |  |

|       | Ans: B                                                                   |                                                               |  |  |

|       | (26) <sub>10</sub> in BCD is (0010)<br>Add 011 to each BCD 02            |                                                               |  |  |

| Q.44  | How many AND gates are requir                                            |                                                               |  |  |

|       | (A) 4<br>(C) 3                                                           | (B) 5<br>(D) 2                                                |  |  |

|       | Ans: D To realize Y = CD + EF + Two AND gates                            | G are required (for CD & EF).                                 |  |  |

| Q.45  | How many select lines will a 16 to                                       | to 1 multiplexer will have                                    |  |  |

| Q. 13 | (A) 4                                                                    | (B) 3                                                         |  |  |

|       | (C) 5                                                                    | <b>(D)</b> 1                                                  |  |  |

|       | Ans: A  In 16 to 1 MHY four select                                       | lines will be required to select $16 (2^4)$ inputs.           |  |  |

|       | iii 10 to 1 WOA 10th select                                              | lines will be required to select 10 (2 ) inputs.              |  |  |

| Q.46  | How many flip flops are required                                         |                                                               |  |  |

|       | (A) 10                                                                   | (B) 3<br>(D) 2                                                |  |  |

|       | (C) 4                                                                    | <b>(D)</b> 2                                                  |  |  |

|       | Ans: C Decade counter counts 10 Thus four FlipFlop's are rec             | states from 0 to 9 ( i.e. from 0000 to 1001 ) quired.         |  |  |

| Q.47  | Which TTL logic gate is used for                                         | wired ANDing                                                  |  |  |

|       | <ul><li>(A) Open collector output</li><li>(C) Tri state output</li></ul> | <ul><li>(B) Totem Pole</li><li>(D) ECL gates</li></ul>        |  |  |

|       | Ans: A Open collector output.                                            |                                                               |  |  |

| Q.48  | CMOS circuits consume power                                              |                                                               |  |  |

|       | <ul><li>(A) Equal to TTL</li><li>(C) Twice of TTL</li></ul>              | <ul><li>(B) Less than TTL</li><li>(D) Thrice of TTL</li></ul> |  |  |

|       | Ans: B As in CMOS one device is C                                        | ON & one is Always OFF so power consumption is low            |  |  |

| Q.49  | In a RAM, information can be sto  (A) By the user, number of ti          |                                                               |  |  |

- **(B)** By the user, only once.

- (C) By the manufacturer, a number of times.

- **(D)** By the manufacturer only once.

### Ans: A

RAM is used by the user, number of times.

**Q.50** The hexadecimal number for  $(95.5)_{10}$  is

**(A)**  $(5F.8)_{16}$

**(B)**  $(9A.B)_{16}$

(C)  $(2E.F)_{16}$

**(D)**  $(5A.4)_{16}$

Ans: A

$$(95.5)_{10} = (5F.8)_{16}$$

Integer part

$$| 16 | 95$$

$$| 16 | 5 | 15$$

$$| 0 | 5$$

Fractional part 0.5x16=8.0

**Q.51** The octal equivalent of  $(247)_{10}$  is

**(A)**  $(252)_8$

**(B)**  $(350)_8$

**(C)**  $(367)_8$

**(D)**  $(400)_8$

Ans: C

$$(247)_{10} = (367)_8$$

- Q.52 The chief reason why digital computers use complemented subtraction is that it

- **(A)** Simplifies the circuitry.

- **(B)** Is a very simple process.

- (C) Can handle negative numbers easily.

- (D) Avoids direct subtraction.

Ans: C

Using complement method negative numbers can also be subtracted.

Q.53 In a positive logic system, logic state 1 corresponds to

- (A) positive voltage

- (B) higher voltage level

- (C) zero voltage level

- (D) lower voltage level

Ans: B

We decide two voltages levels for positive digital logic. Higher voltage represents logic 1 & a lower voltage represents logic 0.

- Q.54 The commercially available 8-input multiplexer integrated circuit in the TTL family is

- **(A)** 7495.

**(B)** 74153.

**(C)** 74154.

**(D)** 74151.

Ans: B

MUX integrated circuit in TTL is 74153.

- Q.55 CMOS circuits are extensively used for ON-chip computers mainly because of their extremely

- (A) low power dissipation.

- **(B)** high noise immunity.

- **(C)** large packing density.

- (D) low cost.

Ans: C

Because CMOS circuits have large packing density.

- **Q.56** The MSI chip 7474 is

- (A) Dual edge triggered JK flip-flop (TTL).

- **(B)** Dual edge triggered D flip-flop (CMOS).

- (C) Dual edge triggered D flip-flop (TTL).

- **(D)** Dual edge triggered JK flip-flop (CMOS).

- Ans: C

MSI chip 7474 dual edge triggered D Flip-Flop.

- Q.57 Which of the following memories stores the most number of bits

- (A) a  $5M \times 8$  memory.

- **(B)** a  $1M \times 16$  memory.

- (C) a  $5M \times 4$  memory.

- **(D)** a  $1M \times 12$  memory.

## Ans: A

$$5Mx8 = 5 \times 220 \times 8 = 40M \text{ (max)}$$

- Q.58 The process of entering data into a ROM is called

- (A) burning in the ROM

- **(B)** programming the ROM

- (C) changing the ROM

- (D) charging the ROM

### Ans: B

The process of entering data into ROM is known as programming the ROM.

- Q.59 When the set of input data to an even parity generator is 0111, the output will be

- **(A)** 1

**(B)** 0

**(C)** Unpredictable

(D) Depends on the previous input

### Ans: B

In even parity generator if number of 1 is odd then output will be zero.

| Q.60         | The number 140 in octal is equi                                                                                        |                                                                                  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

|              | <b>(A)</b> $(96)_{10}$ .                                                                                               | <b>(B)</b> $(86)_{10}$ .                                                         |  |  |

|              | (C) $(90)_{10}$ .                                                                                                      | <b>(D)</b> none of these.                                                        |  |  |

|              | Ans: A<br>$(140)_8 = (96)_{10}$<br>$1 \times 8^2 + 4 \times 8 + 0 \times 1$                                            | = 64 + 32 = 96                                                                   |  |  |

| Q.61         | The NOR gate output will be lo (A) 00 (C) 10                                                                           | w if the two inputs are (B) 01 (D) 11                                            |  |  |

|              | Ans: B, C, or D O/P is low if any of the I/                                                                            | P is high                                                                        |  |  |

| Q.62         | Which of the following is the fa                                                                                       | stest logic?                                                                     |  |  |

|              | (A) ECL                                                                                                                | (B) TTL                                                                          |  |  |

|              | (C) CMOS                                                                                                               | (D) LSI                                                                          |  |  |

|              | Ans: A                                                                                                                 |                                                                                  |  |  |

| Q.63         | How manyflip-flops are required to construct mod 30 counter                                                            |                                                                                  |  |  |

|              | (A) 5                                                                                                                  | <b>(B)</b> 6                                                                     |  |  |

|              | (C) 4                                                                                                                  | <b>(D)</b> 8                                                                     |  |  |

|              | Ans: A  Mod - 30 counter +/- needs  Mod - N counter counts tot  To count 'N' distinguished  For eg. Mod 8 counter requ | al ' N ' number of states.<br>states we need minimum n FlipFlop's as $[N = 2^n]$ |  |  |

| Q.64         | How many address hits are requ                                                                                         | ired to represent a 32 K memory                                                  |  |  |

| <b>2.</b> 0. | (A) 10 bits.                                                                                                           | ( <b>B</b> ) 12 bits.                                                            |  |  |

|              | (C) 14 bits.                                                                                                           | <b>(D)</b> 16 bits.                                                              |  |  |

|              | Ans: D<br>$32K = 2^5 \times 2^{10} = 2^{15}$ ,<br>Thus 15 address bits are 1                                           | required, Only 16 bits can address it.                                           |  |  |

| Q.65         | The number of control lines for <b>(A)</b> 2.                                                                          | 16 to 1 multiplexeris (B) 4.                                                     |  |  |

|              | (C) 3.                                                                                                                 | <b>(D)</b> 5.                                                                    |  |  |

|              | Ans: B As $16 = 2^4$ , 4 Select lines                                                                                  | are required.                                                                    |  |  |

| Q.66         | Which of following requires refi                                                                                       | reshing?                                                                         |  |  |

| ~·••         | (A) SRAM.                                                                                                              | (B) DRAM.                                                                        |  |  |

**(C)** ROM.

(D) EPROM.

Ans: B

- Q.67 Shifting a register content to left by one bit position is equivalent to

- (A) division by two.

- **(B)** addition by two.

- **(C)** multiplication by two.

- **(D)** subtraction by two.

Ans:C

- Q.68 For JK flip flop with J=1, K=0, the output after clock pulse will be

- **(A)** 0.

- **(B)** 1.

- (C) high impedance.

- (D) no change.

Ans: B

- Q.69 Convert decimal 153 to octal. Equivalent in octal will be

- (A)  $(231)_8$ .

**(B)**  $(331)_8$ .

(C)  $(431)_8$ .

(D) none of these.

Ans: A

$$(153)_{10} = (231)_8$$

| 8 | 153 | 1 4 |

|---|-----|-----|

| 8 | 19  | 3   |

| 8 | 2   | 2   |

|   |     |     |

- **Q.70** The decimal equivalent of  $(1100)_2$  is

- **(A)** 12

**(B)** 16

**(C)** 18

**(D)** 20

Ans: A

$$(1100)_2 = (12)_{10}$$

- **Q.71** The binary equivalent of  $(FA)_{16}$  is

- **(A)** 1010 1111

**(B)** 1111 1010

**(C)** 10110011

(D) none of these

Ans: B

$$(FA)_{16} = (111111010)_{10}$$

- Q.72 The output of SR flip flop when S=1, R=0 is

- **(A)** 1

**(B)** (

(C) No change

**(D)** High impedance

|      | Ans: A As for the SR flip-flop S=set in                                                                           | put R=reset input ,when S=1, R=0, Flip-flop will be set.               |

|------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Q.73 | The number of flip flops contained in (A) 2. (C) 4.                                                               | (B) 3. (D) 10.                                                         |

|      | Ans: A                                                                                                            |                                                                        |

| Q.74 | The number of control lines for 32 to 1 (A) 4. (C) 16.                                                            | multiplexeris (B) 5. (D) 6.                                            |

|      | Ans: B  The number of control lines for lines are required.                                                       | 32 (2 <sup>5</sup> ) and to select one input among them total 5 select |

| Q.75 | How many two-input AND and OR ga (A) 2,2. (C) 3,3.                                                                | tes are required to realize Y=CD+EF+G  (B) 2,3.  (D) none of these.    |

|      | Ans: A Y=CD+EF+G Number of two input AND gates=2 Number of two input OR gates = 2 One OR gate to OR CD and EF and |                                                                        |

| Q.76 | <ul><li>Which of following can not be accessed</li><li>(A) DRAM.</li><li>(C) ROM.</li></ul>                       | ed randomly (B) SRAM. (D) Magnetic tape.                               |

|      | Ans: D  Magnetic tape can only be access                                                                          | ssed sequentially.                                                     |

| Q.77 | The excess-3 code of decimal 7 is repr<br>(A) 1100.<br>(C) 1011.                                                  | resented by (B) 1001. (D) 1010.                                        |

|      | Ans: D An excess 3 code is always equa                                                                            | al to the binary code +3                                               |

| Q.78 | When an input signal A=11001 is appl (A) 00111. (C) 10101.                                                        | ied to a NOT gate serially, its output signal is (B) 00110. (D) 11001. |

|      | Ans: B As A=11001 is serially applied to                                                                          | a NOT gate, first input applied will be LSB 00110.                     |

| Q.79 | The result of adding hexadecimal numb (A) DD. (C) F0.                                                                                                                                                                                                                                                 | per A6 to 3A is (B) E0. (D) EF.                                                                                                                 |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

|      | Ans: B                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |  |

| Q.80 | A universal logic gate is one, which can the following is a universal logic gate?  (A) OR  (C) XOR                                                                                                                                                                                                    | <ul><li>(B) AND</li><li>(D) NAND</li></ul>                                                                                                      |  |

|      | Ans: D  NAND can generate any logic fund                                                                                                                                                                                                                                                              | ction.                                                                                                                                          |  |

| Q.81 | The logic 0 level of a CMOS logic dev.  (A) 1.2 volts  (C) 5 volts                                                                                                                                                                                                                                    | (B) 0.4 volts (D) 0 volts                                                                                                                       |  |

|      | Ans: D CMOS logic low level is 0 volts ap                                                                                                                                                                                                                                                             | prox.                                                                                                                                           |  |

| Q.82 | <ul> <li>Karnaugh map is used for the purpose of</li> <li>(A) Reducing the electronic circuits used.</li> <li>(B) To map the given Boolean logic function.</li> <li>(C) To minimize the terms in a Boolean expression.</li> <li>(D) To maximize the terms of a given a Boolean expression.</li> </ul> |                                                                                                                                                 |  |

|      | Ans: C                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |  |

| Q.83 | <ul> <li>A full adder logic circuit will have</li> <li>(A) Two inputs and one output.</li> <li>(B) Three inputs and three outputs.</li> <li>(C) Two inputs and two outputs.</li> <li>(D) Three inputs and two outputs.</li> </ul>                                                                     |                                                                                                                                                 |  |

|      |                                                                                                                                                                                                                                                                                                       | es and it will also accounts the carry input generated in ts and two outputs (Sum and Carry) are there.                                         |  |

| Q.84 |                                                                                                                                                                                                                                                                                                       | ip-flop with propagation delay of 75 nanoseconds. The effrequency of the input signal which can be used for eximately  (B) 500 MHz.  (D) 4 MHz. |  |

|      | Ans: A                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |  |

Maximum time taken for all flip-flops to stabilize is  $75 \text{ns} \times 8 + 50 = 650 \text{ns}$ . Frequency of operation must be less than 1/650 ns = 1.5 MHz.

- **Q.85** The output of a JK flipflop with asynchronous preset and clear inputs is '1'. The output can be changed to '0' with one of the following conditions.

- (A) By applying J = 0, K = 0 and using a clock.

- **(B)** By applying J = 1, K = 0 and using the clock.

- (C) By applying J = 1, K = 1 and using the clock.

- **(D)** By applying a synchronous preset input.

## Ans: C

Preset state of JK Flip-Flop =1

With J=1 K=1 and the clock next state will be complement of the present state.

- **O.86** The information in ROM is stored

- (A) By the user any number of times.

- **(B)** By the manufacturer during fabrication of the device.

- **(C)** By the user using ultraviolet light.

- **(D)** By the user once and only once.

Ans: B

- **Q.87** The conversation speed of an analog to digital converter is maximum with the following technique.

- (A) Dual slope AD converter.

- **(B)** Serial comparator AD converter.

- (C) Successive approximation AD converter.

- (D) Parallel comparator AD converter.

Ans: D

- Q.88 A weighted resistor digital to analog converter using N bits requires a total of

- (A) N precision resistors.

- **(B)** 2N precision resistors.

- (C) N + 1 precision resistors.

- **(D)** N-1 precision resistors.

Ans: A

- **Q.89** The 2's complement of the number 1101110 is

- **(A)** 0010001.

**(B)** 0010001.

**(C)** 0010010.

(D) None.

Ans: C

1's complement of 1101110 is = 0010001

Thus 2's complement of 1101110 is = 0010001 + 1 = 0010010

- **Q.90** The decimal equivalent of Binary number 10101 is

- **(A)** 21

**(B)** 31

**(C)** 26

**(D)** 28

Ans: A

$$1x2^4 + 0x2^3 + 1x2^2 + 0x2^1 + 1x2^0$$

= 16 + 0 + 4 + 0 + 1 = 21.

Q.91 How many two input AND gates and two input OR gates are required to realize

Y = BD + CE + AB

**(A)** 1, 1

**(B)** 4, 2

**(C)** 3, 2

**(D)** 2, 3

Ans: A

There are three product terms, so three AND gates of two inputs are required. As only two input OR gates are available, so two OR gates are required to get the logical sum of three product terms.

- Q.92 How many select lines will a 32:1 multiplexer will have

- **(A)** 5.

**(B)** 8.

**(C)** 9.

**(D)** 11.

Ans: A

For 32 inputs, 5 select lines will be required, as  $2^5 = 32$ .

- Q.93 How many address bits are required to represent 4K memory

- (A) 5 bits.

**(B)** 12 bits.

**(C)** 8 bits.

**(D)** 10 bits.

Ans: B

For representing 4K memory, 12 address bits are required as  $4K = 2^2 \times 2^{10} = 2^{12}$   $(1K = 1024 = 2^{10})$

- **Q.94** For JK flipflop J = 0, K=1, the output after clock pulse will be

- **(A)** 1.

(B) no change.

**(C)** 0.

(**D**) high impedance.

Ans: C

J=0, K=1, these inputs will reset the flip-flop after the clock pulse. So whatever be the previous output, the next state will be 0.

- Q.95 Which of following are known as universal gates

- (A) NAND & NOR.

- (B) AND & OR.

**(C)** XOR & OR.

(D) None.

Ans: A

NAND & NOR are known as universal gates, because any digital circuit can be realized completely by using either of these two gates.

- Q.96 Which of the following memories stores the most number of bits

- (A)  $64K \times 8$  memory.

- **(B)**  $1M \times 8$  memory.

(C)  $32M \times 8$  memory.

**(D)**  $64 \times 6$  memory.

Ans: C

32M x 8 stores most number of bits

$$2^5 \times 2^{20} = 2^{25}$$

$$(1M = 2^{20} = 1K \times 1K = 2^{10} \times 2^{10})$$

- Q.97 Which of following consume minimum power

- (A) TTL.

(B) CMOS.

**(C)** DTL.

**(D)** RTL.

Ans: B

CMOS consumes minimum power as in CMOS one p-MOS & one n-MOS transistors are connected in complimentary mode, such that one device is ON & one is OFF.

- Q.98 In the decimal numbering system, what is the MSD?

- a. the middle digit of a stream of numbers

- B. the digit to the right of the decimal point

- c. the last digit on the right

- d. the digit with the most weight

Ans: D

The digit with the most weight

- Q.99 Which of the following statements does NOT describe an advantage of digital technology? a. the values may vary over a continuous range.

- b. the circuits are less affected by noise.

- c. the operation can be programmed.

- d. information storage is easy.

Ans: A

- a. the values may vary over a continuous range.

- Q.100 The generic array logic (GAL) device is \_\_\_\_\_\_.

- a. one-time programmable

- b. reprogrammable

- c. a cmos device

- d. reprogrammable and a cmos device

Ans: B

b. reprogrammable